本周数字电路课程老师布置了一个利用verilog语言进行数值比较器波形仿真的作业。可以利用Modelsim或者Vivado实现。由于Vivado默认安装大小就有将近30个GB(2018版好像是27GB左右,2014版是12.68GB,这版本的容量增速跟maltab有得一拼啊),因此之前装了之后不太会使用便又卸了。最近刚好趁着双十一降价给自己的laptop加了一个SSD,因此正好赶快学习一下如何使用。有关如何给笔记本加装SSD的问题,这里有两个视频可以解决,安装准备与步骤、安装后点亮磁盘。

References:

电子文献:

https://blog.csdn.net/qq_41154156/article/details/80989125

https://wenku.baidu.com/view/0294cbb3bb4cf7ec4bfed01a.html

关于vivado

相比于Modelsim,Vivado的UI还是要舒服许多的,有点像Multisim之于Pspice。关于Vivado的使用,上面参考的文章中的步骤比较详细,照做一遍之后基本就会了。

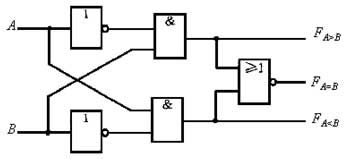

1位数值比较器

1位数值比较器的逻辑图如下:

使用verilog代码实现:

1 | module _1bit_Comp( |

为了输出仿真波形,新建一个仿真文件:

1 | module simulateFile(); |

其中,过程赋值语句always只能给寄存器类型变量赋值,因此,在这里A、B要定义为reg类型。

这里“#50”表示延时,使用{A, B}使AB变成二进制数,方便生成所有不同的输入,在这里即00、01、10、11。

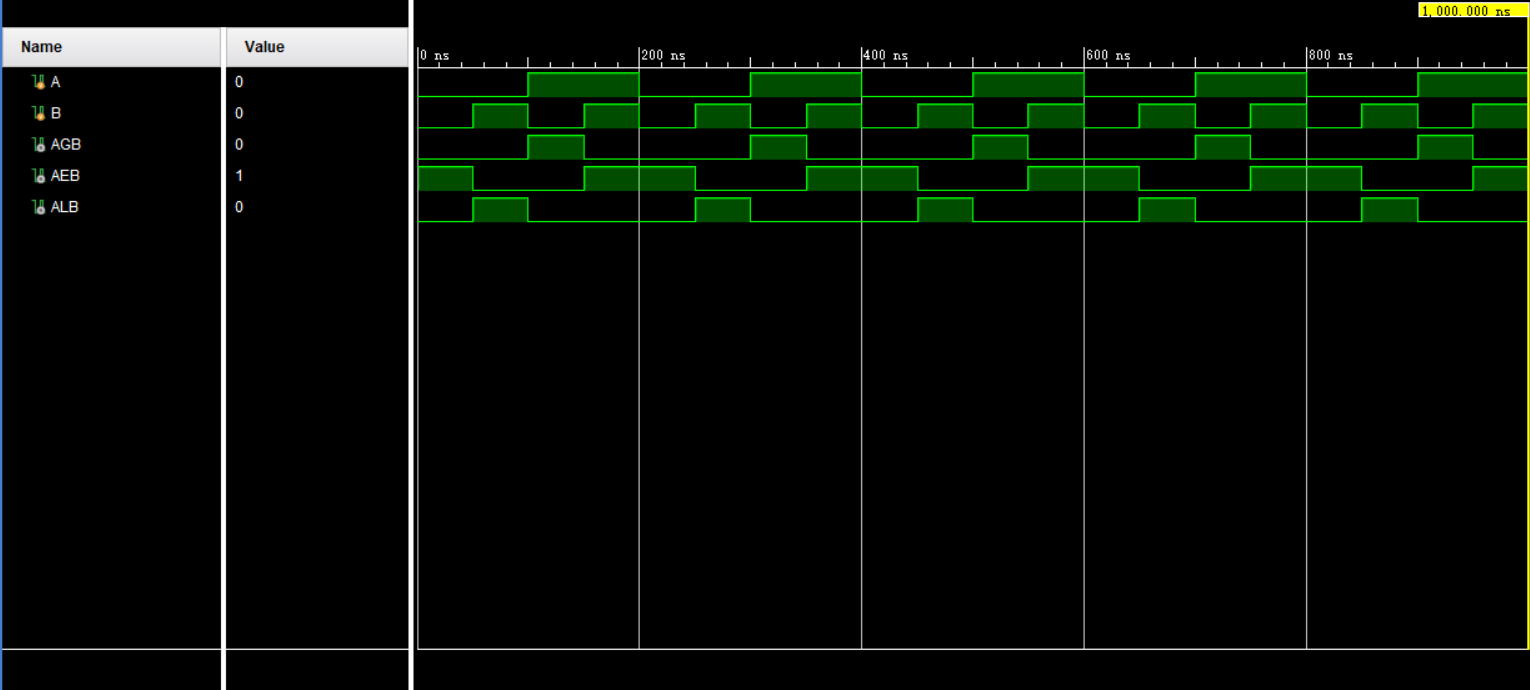

Run Simulation,输出波形:

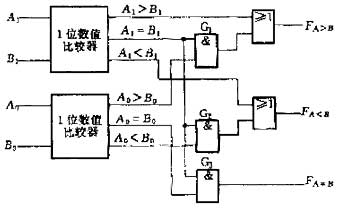

2位数值比较器

2位数值比较器的逻辑图如下:

使用verilog代码,调用1位数值比较器,实现2位数值比较器如下:

1 | module _2bit_Comp( |

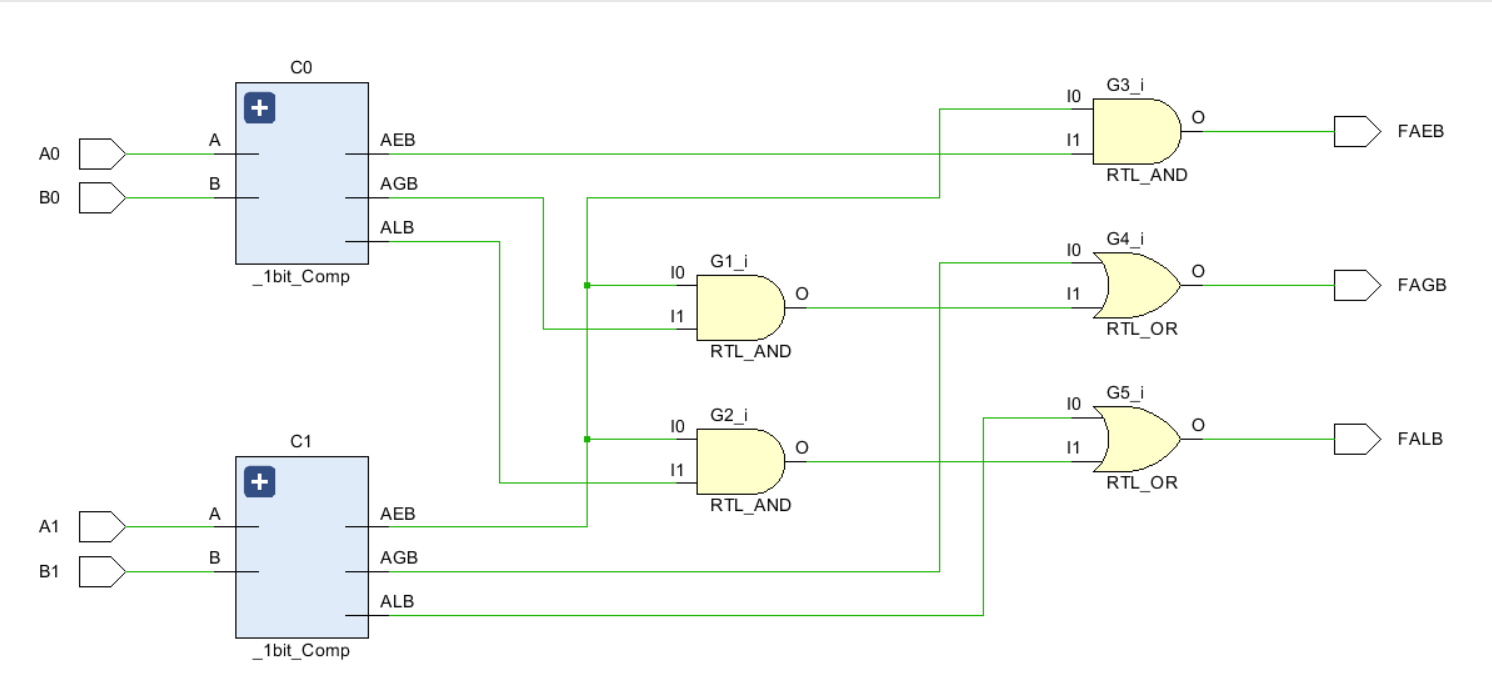

可以使用RTL ANALYSIS来仿真出2位数值比较器的RTL schematic电子原理图。

类似的,编写仿真文件:

1 | module simulateAgain(); |

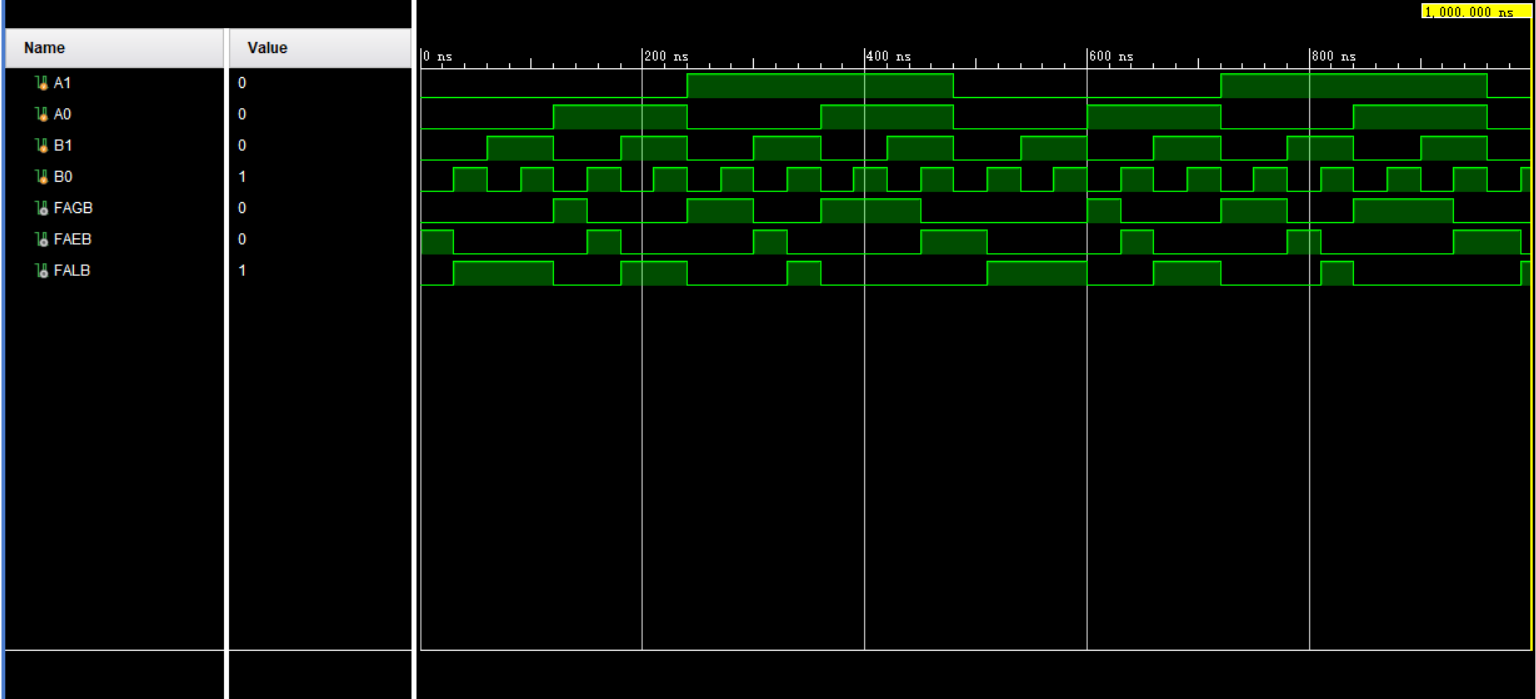

Run Simulation,输出波形:

出现的问题

报错:[Synth 8-439] module’xxx’not found

当初遇到这个问题后,我的第一反应是上网搜索原因。得到的解释有模块未添加、IP未正确设置等。

对照网上的解决方案之后,我发现除了我无法理解的,网上所述的问题我都不存在。于是我只好独立进行思考。

果然,我还犯不了像网上那样“高级”的错误。错误的原代码如下:1

2not n0(Anot, A);

n1(Bnot, B);报错:[Synth 8-439] module’n1’not found。

当我调用门的时候,由于内部变量换行导致我将逗号误用成了分号,因此导致分号之后的变量not found,修改后错误即可解决。

其实,这个问题仔细观察即可发觉,相比于n1,同样格式的n0就没有报错,那么很有可能错误就在两者之间。ERROR: [Common 17-39] ‘xxx’ failed due to earlier errors

这是我在执行仿真文件时遇到的error。仔细检查后,发现错误也与上一个问题相同。由于我在设计完电路后没有Run Synthesis综合并生成网表文件来进行检验,也没有进行其它的仿真操作,因此之前并没能发现这个问题。于是最后当调用该电路的仿真文件开始运行时就会报告这样的错误。

要注意的点

- 和matlab中函数文件的要求类似,verilog定义模块时,需要新建的模块文件名称与模块的文件名称一致。例如,我上面的1位数值比较器module名为_1bit_Comp,那么对应的文件名就应该是_1bit_Comp.v。此外,每个模块应使用一个文件来表示,且一个文件最多能表示一个模块(可以在其中调用其它模块,这点和matlab很像),两者呈一一对应关系。

- 新建project时,如要从RTL代码开始综合,就选择RTL project(默认的这个)。要注意的是,下面的“Do not specify sources at this time”(此时不定义源文件)可以勾上。否则,下一步会进入添加source file。

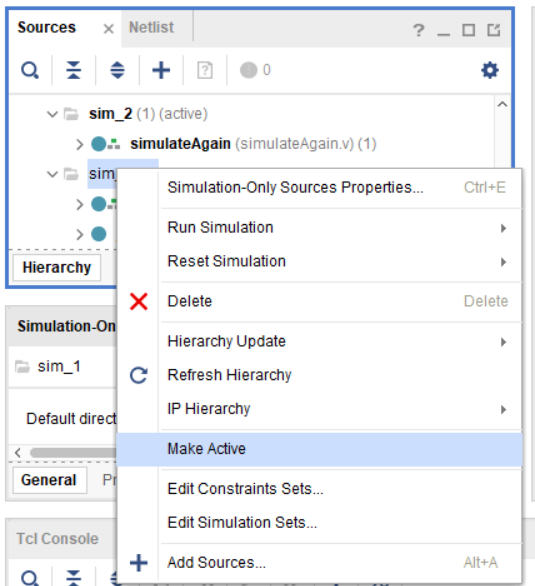

- 如果在一个project中已经建立了一个仿真文件,那么当你新建一个仿真文件时,需要建立在create的new file内,这样在后面对不同的仿真文件进行仿真时可以将对应的文件夹依次分别激活。

- 在source窗口中,一般情况下,Vivado会自动加粗识别出来的top module,同时对应module名称前面也会有一个二叉树状的图标表示这是顶层模块。有时候,软件也会识别错误或者与实际需求不符,这时候我们可以右键想要置顶的module,在弹出的菜单中点击Set As Top将其设为顶层。

- 当在同一个project中创建了多个仿真文件时,如要在进行完一次仿真之后对另一个仿真文件,需要对对应的文件夹进行激活。方法是右键仿真文件,然后在弹出的菜单中点击Make Active即可。

加装固态盘

前文提到给笔记本加装SSD,给了两个示范视频,这里我还是想再稍稍补充一下关于加装固态盘的一些事情。

首先必须确保自己的本有空位。我使用的是小电池版本,因此有一整个2.5英寸7mm的硬盘位,这个请在决定购买新的硬盘前和卖家自己核对确认。如果还是不放心,那么最好亲自拆开查看,眼见为实嘛。要注意的是,必须使用完全对应规格的螺丝刀(比如我使用的是梅花T5螺丝刀),否则很容易发生滑丝,即螺牙连接处由于受力过大或其它原因导致螺牙磨损而使螺牙无法咬合,这会为今后的拆机带来不必要的麻烦。

上面是我买的固态盘和数据线,相同或者类似机型的可以参考一下。在到货之后我发现,我所买的闪迪SSD较7mm稍薄些,因此平时拿动时(一般较大幅度翻动laptop时)会感到里面有东西松动的响声,不过使用至今没遇到任何问题。另外,为了适配各类硬盘,数据线的长度也有可能不能完全匹配,其实也没有关系,稍稍用力将数据线对应接头按入SATA3接口并用架子将固态盘固定即可。相比移动硬盘的USB接口,内置固态的SATA3读取速度还是相当不错的。