继上一篇logisim笔记:基本使用及运动码表的实现,我还使用了硬件描述语言对同样需求的运动码表进行了实现,那么就在这里一并也总结一下吧。

References:

电子文献:

https://blog.csdn.net/leon_zeng0/article/details/78441871

https://www.cnblogs.com/douzi2/p/5147151.html

https://blog.csdn.net/FPGADesigner/article/details/82425612

整体设计

由于需求与使用Logisim实现时一致,因此我的设计思路也基本沿用上一篇博文中提到的方案。但是要注意的是,这里的000状态并不在作为按键抬起之后的中间态,而是进入系统时的一个默认初始状态。

Vivado中一些高亮的含义

在具体的代码之前,我还想先归纳一下本次实践过程中遇到的和发现的Vivado中一些高亮提醒的含义。

土黄色高亮

土黄色高亮出现的原因主要可能是下面三种情况:- 定义重复。

- 定义放在了调用处的后面(identifier used before its declaration)。

- 声明残缺(empty statement)。

蓝色高亮

- 含有undeclared symbol。

- 和上面土黄色高亮相搭配出现,有定义重复时指明重复定义的位置。

16位数值比较器

该模块用于比较两个16位二进制数的大小,以确定是否需要存入记录的数据。代码如下:

1 | module _16bit_Comp( |

16位寄存器

TMRecord表示码表暂停时的读数,regRecord表示寄存器中已经存储的记录,初始值为9999。控制信号有使能信号和reset信号。当收到reset信号时,直接将记录改为9999。当有使能信号时,将TMRecord记录下来。代码如下:

1 | module _16bit_Reg( |

数码管显示驱动

将BCD码转化为7位二进制数,即对应7段数码管,用于显示。

1 | module watchDrive( |

顶层文件

该部分主要包括对各个变量的定义和初始化;状态转换,即共设计了5种状态,对应不同的功能,当按下不同按键时,选择对应的状态并作为次态;数码管的显示与进位,即对数码管4个位置依次改动,从低位开始计算,当进位时产生进位信号到下一位。当有重置信号(这里使用的是reset和start的上升沿)时清零。

1 |

|

仿真文件

最后我们还需要自行编写一个仿真文件。

1 | module simulateFile(); |

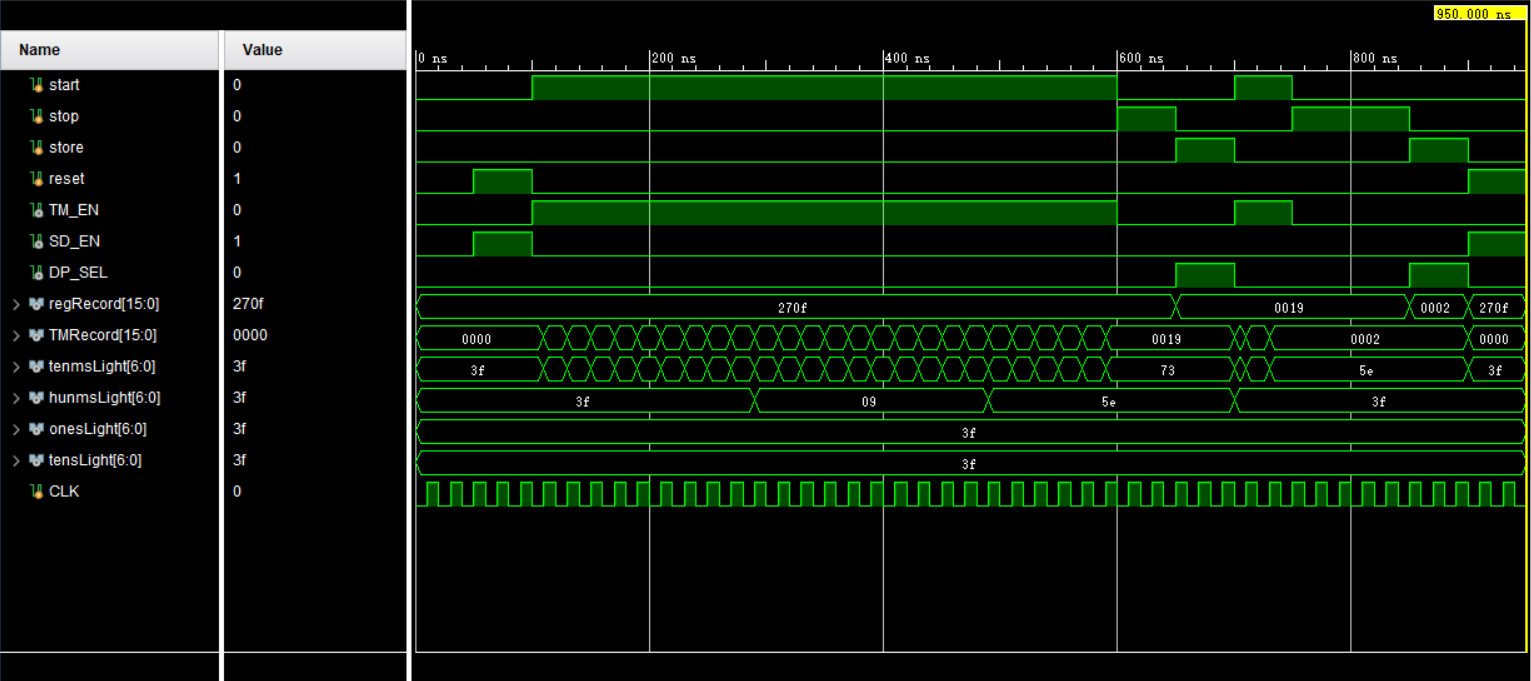

仿真结果

Run simulation,得到如下输出波形图。